This project was undertaken primarily to ease the learning curve for new RMIT students implementing control systems on new UAV configurations. Although FPGAs bring many performance and flexibility benefits for research applications. Learning FPGA development along with the obstructive toolchain by myself was very challenging.

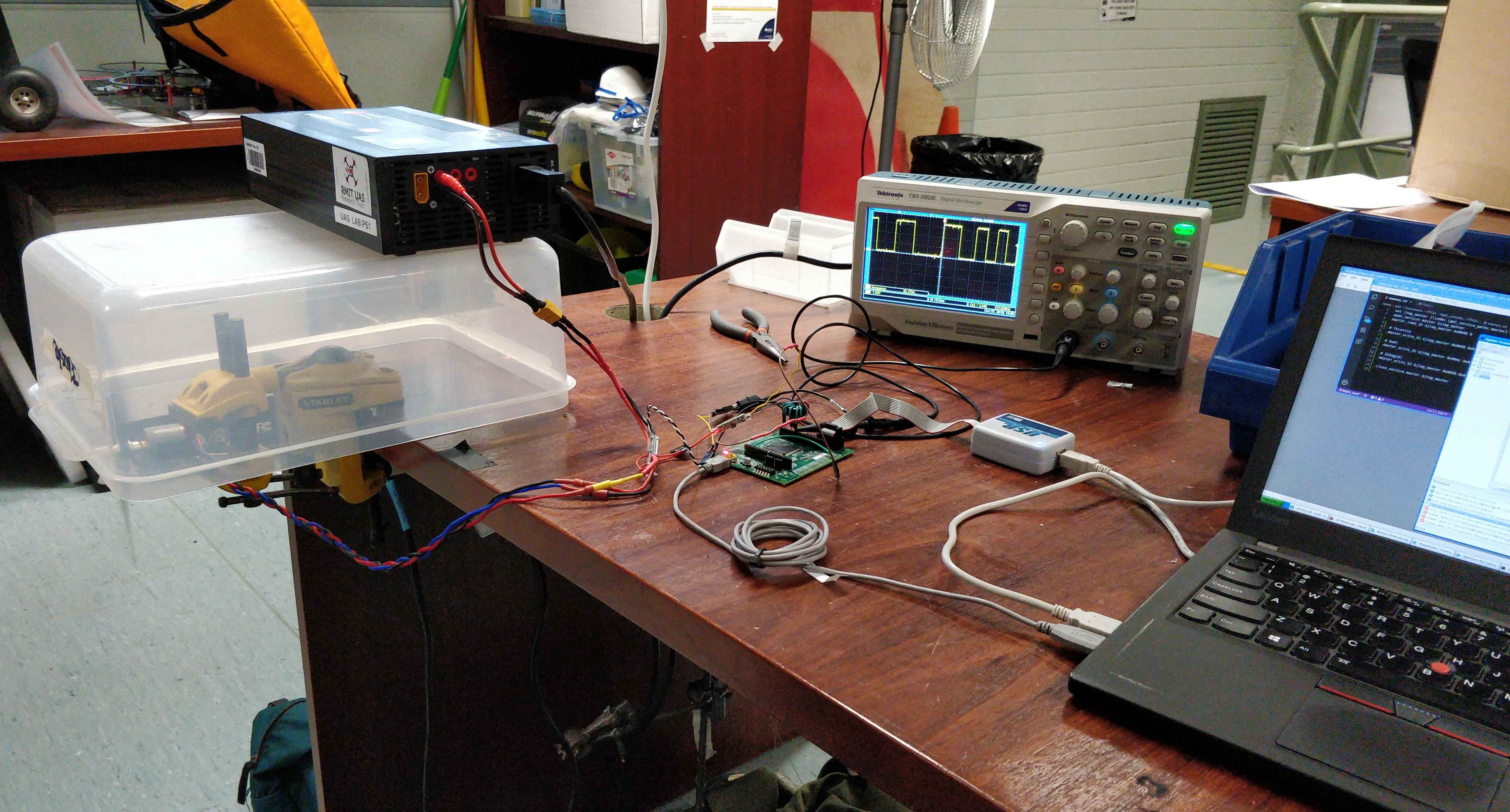

The setup for testing ESC signal output and closed loop control. With the Altera/Intel FPGA visible in the center, and the propeller test stand on the left

The setup for testing ESC signal output and closed loop control. With the Altera/Intel FPGA visible in the center, and the propeller test stand on the left

For my final year project I created a FPGA based hardware platform for use in Multirotor UAVs. I had no experience with FPGA development and no other students to work with. Which made development and debugging very challenging. However my supervisor and I came up with a really exciting design, and my enthusiasm for the project carried me through many weeks of tedious problem solving.

Along the way I learning a lot about hardware debugging and the general FPGA design concepts.

Quick Feature Summary

- Offload interrupt driven tasks into hardware, reducing software complexity

- Timers

- Sensor Data Preprocessing

- Manage peripheral output postprocessing

- ESC throttle

- Perform closed loop control of propeller speed

- Offload complex recurring operations into hardware

- Kalman Filters

- PID Controllers

Please see the report for more information